[ad_1]

Si habéis observado los diferentes diagramas de diferentes arquitecturas, entonces habréis visto como en todos ellos la caché más cercana al procesador, habitualmente llamada caché de primer nivel o L1, se encuentra dividida en dos tipos de memoria distintas llamadas caché de datos y caché de instrucciones. ¿A qué es debido esto? Seguid leyendo y entenderéis el motivo por el cual es una práctica común en todos los diseños

La primera caché en implementarse fue la caché de primer nivel, la cual desde sus inicios siempre ha estado dividida en dos pozos, si alguna vez te has preguntado a que se debe, sigue leyendo y lo entenderás sin ningún problema.

¿Qué es la caché L1 o de primer nivel?

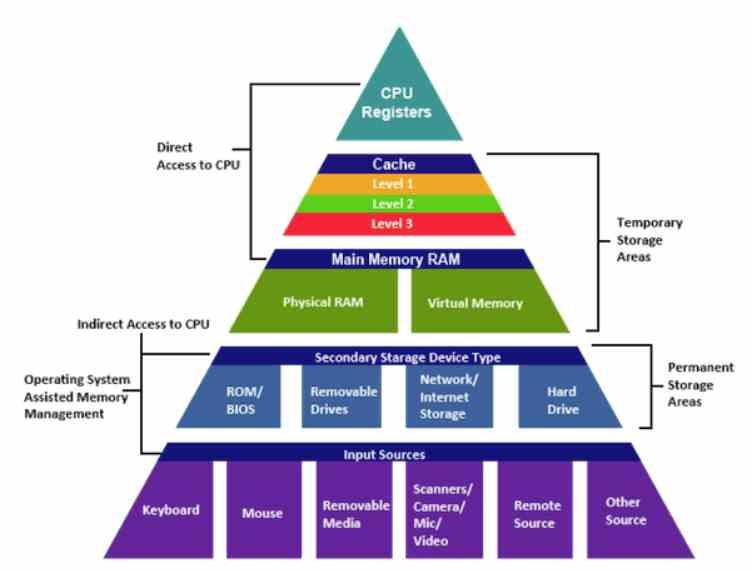

La caché L1 o caché de primer nivel es la más cercana a los núcleos de la CPU y la GPU, por lo que es el tipo de caché con mayor ancho de banda y menor latencia de toda la jerarquía de cachés. Es la primera en la que a la hora de buscar datos en cualquier tipo de procesador el sistema de jerarquía de memoria va a mirar para buscar los datos.

Hay que recordar que la caché no funciona como parte de la RAM sino que copia los datos de la RAM cercanos a los que el procesador se encuentra en ese momento. Una CPU recorre la memoria de manera secuencial las diferentes direcciones de memoria, por lo que para aumentar el rendimiento a la hora de captar datos se hace uso de una memoria caché.

La caché L1 esta siempre separada

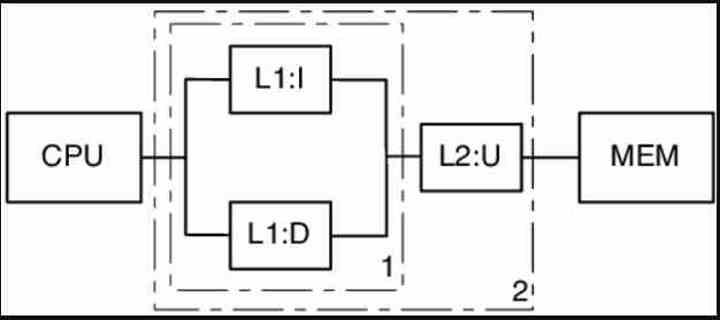

La caché L1 en todos los procesadores está dividida en dos pozos distintos, una caché de datos y una de instrucciones. ¿Qué significa esto? Es sencillo, primero hemos de entender que todas las CPU y GPU utilizan una arquíptera Von Neumann donde las instrucciones que son lo que el procesador ha de hacer, y los datos que son lo que ha de manipular la instrucción, se encuentran en la misma memoria.

Esto se traduce en que las instrucciones tienen una forma en la que x bits del código que forman una instrucción, los primeros bits corresponden el opcode que indican la acción que ha de hacer el procesador, bits que vienen a continuación corresponden a como se a hacer la instrucción y los últimos hacen referencia al dato. Ya sea donde se encuentra el dato o esté en sí mismo, aunque hay instrucciones que carecen de los bits de datos y otros de los bits de modo.

Los datos van desde la RAM a los diferentes niveles de caché, donde datos e instrucciones se mantienen juntos hasta la Caché L2, desde la cual existe un mecanismo que copia la primera parte de la instrucción, el opcode y el modo, en la caché de instrucciones y la otra parte en el Memory Access Register, en el cual se colocan los bits que apuntan a la dirección de memoria. A día de hoy esta última parte es un poco más compleja, pero por motivos didácticos lo vamos a dejar así.

¿A que se debe la separación de la caché?

El motivo de ello es que a nivel interno lo que es la información del opcode de la instrucción se trata diferente al resto. El opcode se trata con el descodificador de instrucciones del procesador. En realidad en todos los procesadores primero se maneja la primera parte de la instrucción y el motivo de ello es muy sencillo. Hay instrucciones que no apuntan a una dirección de memoria sino que incluyen el dato a operar y por tanto no es necesario que el dato se copie en el registro de acceso a la memoria, sino que se copia en un registro especial.

Cuando se necesita buscar un dato en la RAM en un sistema con caché de primer nivel, una vez que el procesador ha comprobado que el opcode corresponde a una instrucción que apunta a un dato en una parte de la memoria, entonces se copia dicha dirección en el MAR, la RAM devolverá el dato en el registro MDR, Memory Data Register, y los mecanismos correspondientes copiaran el dato en el registro correspondiente, normalmente el registro acumulador, que es el que se utiliza para las operaciones aritméticas.

Todo el proceso de descodificación de las instrucciones y búsqueda de datos ocurre en paralelo, con varios accesos a la caché L1 que de hacerse bajo un mismo pozo de memoria acabaría creando una enorme contención a la hora de acceder. Es decir, la caché L1 fue clave para aumentar el rendimiento de los procesadores, siendo el 80486 el primer procesador en PC que lo implemento. En GPUs las cachés de primer nivel se empezaron a implementar a partir de la llegada de las unidades shader en ellas.

The post ¿Por qué la caché L1 de las CPU esta siempre dividida? appeared first on HardZone.

[ad_2]