[ad_1]

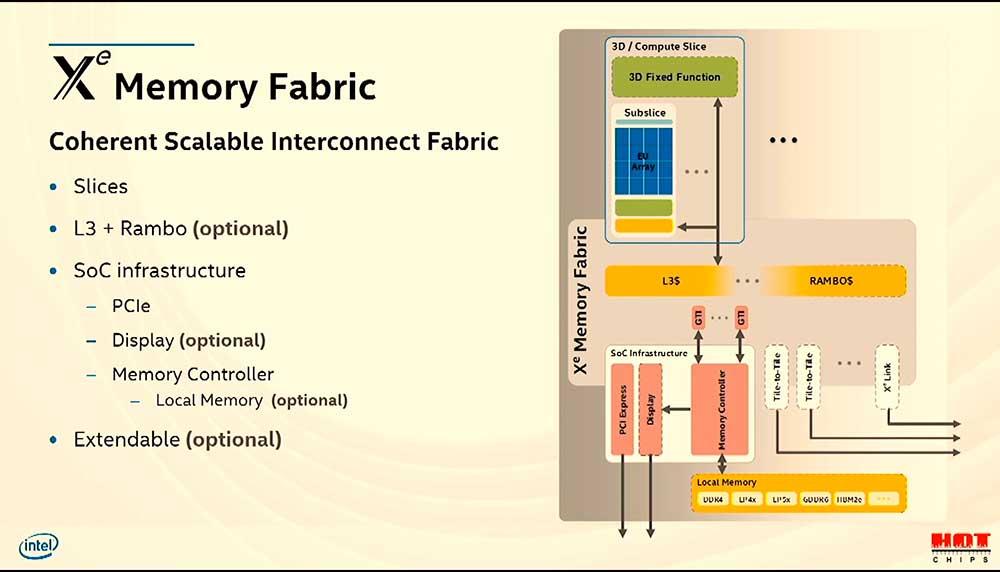

Durante su presentación en 2019 acerca del futuro de la arquitectura Intel Xe, Raja Koduri hizo mención a un tipo de memoria a la que Intel ha bautizo como «Rambo Cache» y que es una de las piezas clave para los Intel Xe. Pero, ¿qué es la Rambo Cache exactamente y cual es su utilidad? Os lo explicamos.

¿Cómo hacemos que una enorme cantidad de chiplets de GPU se comuniquen de manera eficiente entre si? Necesitamos una memoria que haga el trabajo de la intercomunicación y es ahí donde entra la Rambo Cache. Os explicamos como funciona y cual es su función.

Rambo Cache como diferencia entre Xe-HP y Xe-HPC

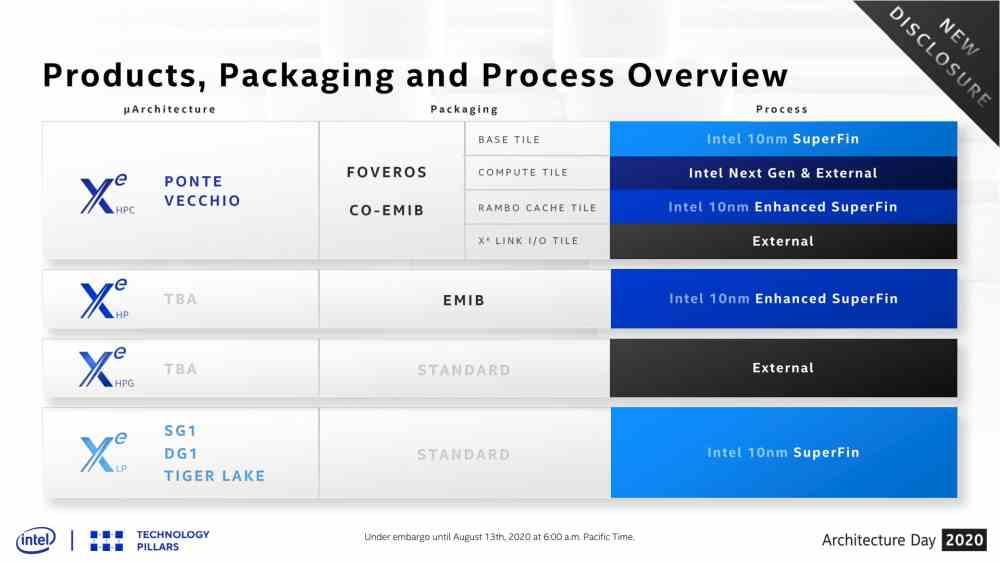

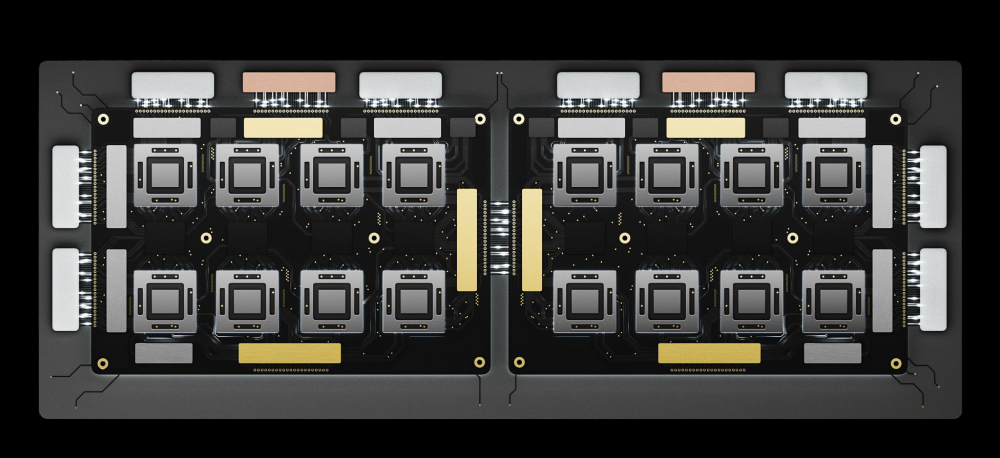

Como se puede ver en la diapositiva de Intel, la Rambo Cache es en si mismo un chip que incluye una memoria en su interior, la cual se va a utilizar en exclusiva en los Intel Xe-HPC para la comunicación entre los diferentes tiles/chiplets. Mientras que el Intel Xe-HP soporta hasta 4 tiles distintos, el Intel Xe-HPC maneja una cantidad de datos mucho más alta, lo que hace necesario este chip de memoria adicional como puente de comunicación para configuraciones sumamente complejas en cuanto a la cantidad de Chiplets de GPU, o tiles como las llama Intel.

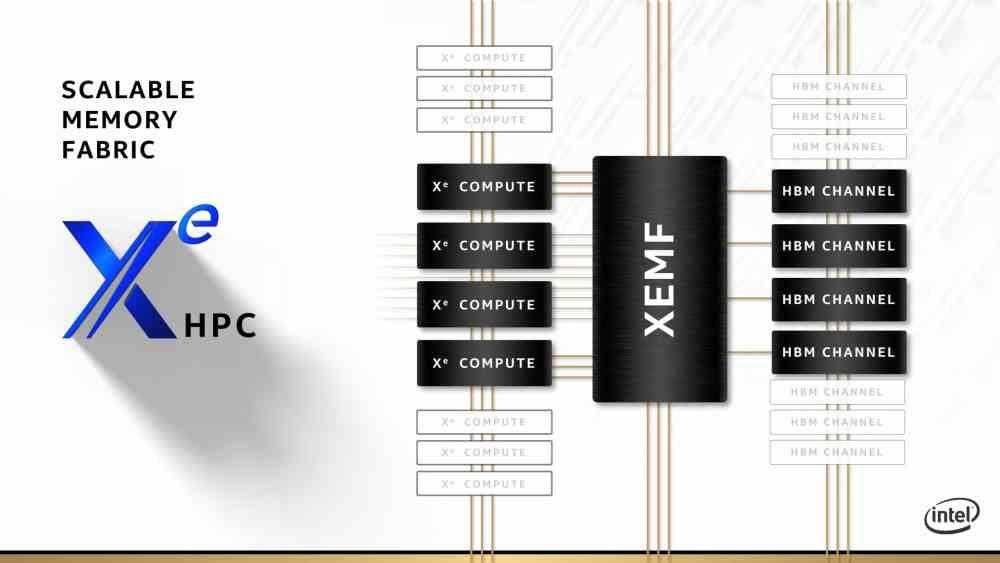

La Rambo Cache se situará entre varios Compute Tiles del Intel Xe-HPC para facilitar la comunicación entre estas. Las Compute Tiles no son otra cosa que GPUs Intel Xe pero especializadas para la computación de alto rendimiento, por lo que las unidades de función fija clásicas en las GPU no estarán en el Intel Xe-HPC por no utilizarse en la computación de alto rendimiento.

No obstante la Rambo Cache va a ser inédita en el resto de los Intel Xe, especialmente los que no se van a basar en varios chiples como es el caso de los Intel Xe-LP e Intel Xe-HPG. En el caso concreto del Intel Xe-HP parece ser que con 4 chiplets no es necesaria la Rambo Cache por el hecho que Interposer da el suficiente ancho de banda para comunicar los diferentes chiplets montados encima del mismo.

El objetivo es llegar al ExaFLOP

Sabemos que el límite en cuanto a la cantidad de chiplets sobre un interposer es de 4 GPUs, pero a partir de una cantidad mayor es cuando la interconexión basada en un interposer EMIB ya no da el suficiente ancho de banda para la comunicación, lo que hace que sea necesario un elemento que cohesione el acceso a la memoria y es ahí donde entraria la Rambo Cache, ya que le permitiría a Intel poder hacer una GPU más compleja que la de 4 chiplets máximo que puede construir con el EMIB.

¿El objetivo? Poder crear un hardware que de manera combinada pueda llegar a 1 PetaFLOP de violencia o dicho de otra manera 1000 TFLOPS. Un rendimiento muy por encima que las GPUs que tenemos en PC, pero es que no hablamos de una GPU para PC sino de un hardware pensado para super-ordenadores, con el objetivo de llegar al hito del ExaFLOP, que son 1000 PetaFLOPS y por tanto 1 millón de TeraFLOPS.

La gran preocupación de los arquitectos de hardware para conseguirlo es el consumo energético, especialmente en la transferencia de datos, a más cálculos más datos se mueven y a más datos más energía. Por eso es importante mantener los datos lo más cercanos de los procesadores y es aquí donde entra la Rambo Cache.

La Rambo Cache como caché de último nivel

Cuando tenemos varios núcleos, tanto si hablamos de una CPU como de una GPU, y queremos que todas ellas acceden al mismo pozo de memoria a nivel tanto de direccionamiento como físico, entonces hace falta una caché de último nivel. Su situación «geográfica» dentro de la GPU es justo antes del controlador de memoria pero después de las caches privadas de cada núcleo.

Las GPUs hoy en día tienen dos niveles de cache como mínimo, el primer nivel es privado de las unidades shader y suele estar conectado a las unidades de texturas. El segundo nivel en cambio es compartido por todos los elementos de una GPU. En este caso son su camino de interconexión para comunicarse, acceder a los datos más recientes y todo ello para no saturar el controlador de la VRAM con peticiones a la misma.

Pero existe un nivel adicional, cuando tenemos varias GPUs completas interconectadas entre si bajo la misma memoria, entonces hace falta un nivel de cache adicional que agrupe los accesos a todas las memorias. Siendo la Rambo Cache de Intel la solución de Intel para unificar el acceso de todas las GPUs que de manera combinada forman Ponte Vecchio.

The post Este es el secreto de Intel para fabricar una GPU gaming con chiplets appeared first on HardZone.

[ad_2]