[ad_1]

La Ley de Moore ha sido el principio rector de la industria de los semiconductores durante más de cincuenta años. Durante treinta de estos últimos años, Robert Chau (actual Director de investigación y componentes en Intel) ha formado parte de la organización de desarrollo de tecnología de Intel, brindándole una vista panorámica de las innovaciones revolucionarias que han permitido mejoras constantes en cuanto a densidad, rendimiento y eficiencia en los transistores. Y según Chau, la Ley de Moore todavía tiene por delante un futuro muy brillante y estamos lejos de llegar al punto de inflexión en el que ya no se pueda cumplir.

En su nivel más simple, la Ley de Moore se refiere a la duplicación de transistores dentro de un chip con cada generación de proceso de fabricación. A lo largo de los años este aumento exponencial en la densidad de transistores se ha mantenido notablemente constante, pero dos cosas han cambiado a lo largo del camino: cómo logramos estos aumentos de densidad y los beneficios que se obtienen a nivel de producto.

El futuro de la Ley de Moore según Robert Chau

Ya se trate de frecuencias más altas y menor consumo de energía o más funcionalidad integrada en un chip, la Ley de Moore se ha adaptado al futuro y ha evolucionado para satisfacer las demandas de cada generación de tecnología, desde mainframes hasta teléfonos móviles. Esta evolución continuará a medida que avancemos hacia una nueva era de datos ilimitados e inteligencia artificial.

¿Qué innovaciones impulsará la Ley de Moore durante la próxima década? Creo que pueden categorizarse colectivamente en dos áreas bastante amplias: escalamiento monolítico y escalamiento del sistema. La escala monolítica puede denominarse la escala «clásica» de la Ley de Moore, con un enfoque en la reducción de los tamaños de los transistores y los voltajes de operación mientras se aumenta el rendimiento de cada transistor. Las mejoras de escala de sistema son las ganancias que nos ayudan a incorporar nuevos tipos de procesadores heterogéneos a través de avances en chiplets, empaquetado y tecnologías de interconexión de chip a chip con alto ancho de banda.

Intel está invirtiendo mucho en investigación para respaldar ambos vectores; en la reunión anual de 2019 de los principales impulsores tecnológicos de procesos de semiconductores del mundo, IEDM en San Francisco, los ingenieros de Intel presentaron casi veinte artículos que demuestran un trabajo innovador que garantiza un futuro brillante para la Ley de Moore en las próximas generaciones. Lo que sigue es un resumen de alto nivel de estas interesantes opciones tecnológicas.

Escala monolítica: una nueva dimensión

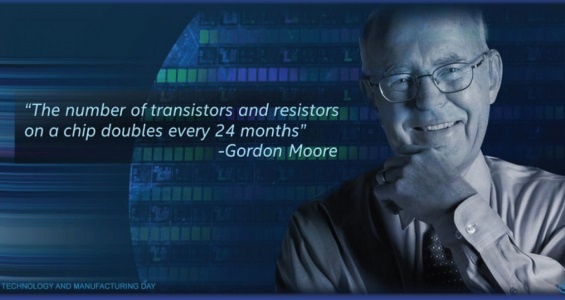

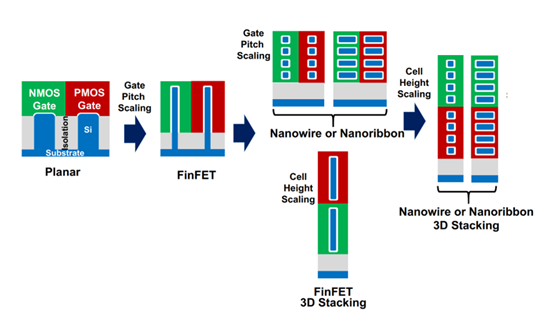

Los procesadores Intel de generaciones actuales se basan en una estructura de transistor conocida como FinFET, en la que la puerta rodea el canal en forma de aleta en tres de sus lados. A medida que los nodos de proceso de Intel han avanzado, han hecho que las aletas sean más altas pero más estrechas, lo que permite reducir la cantidad de aletas necesarias para lograr un determinado nivel de rendimiento.

Si bien FinFET todavía tiene mucha vida por delante, en algún momento del futuro cercano la industria hará la transición a un nuevo tipo de arquitectura de transistores: Gate-All-Around (GAA) FET, en el que la puerta envuelve el canal en todos sus lados. Existen múltiples implementaciones potenciales para GAAFET, desde nanocables delgados hasta nanocintas anchas. Lo que comparten en común es la capacidad de empaquetar más transistores de alto rendimiento en un área determinada, reduciendo así el ancho de las celdas estándar que utilizan nuestros diseñadores para construir nuevos procesadores.

Además de esta nueva arquitectura de transistores, otra forma de impulsar el escalado del área de la celda es mediante el apilamiento vertical de dispositivos de transistores. Los semiconductores modernos se construyen a partir de pares complementarios de transistores cargados negativa y positivamente llamados NMOS y PMOS. La altura de una celda estándar se puede reducir significativamente mediante el apilamiento monolítico de un dispositivo NMOS en la parte superior de un dispositivo PMOS, o viceversa. Esto se puede lograr apilando FinFET, GAAFET o incluso una combinación de ambos.

El apilamiento monolítico de dispositivos de transistores no solo ofrece una densidad mejorada, sino que es una forma interesante de integrar múltiples materiales en un solo sustrato de silicio, lo que proporciona un rendimiento significativamente mejorado y abre la puerta a clases de productos completamente nuevos con una funcionalidad única.

Escalado del sistema: más allá del transistor

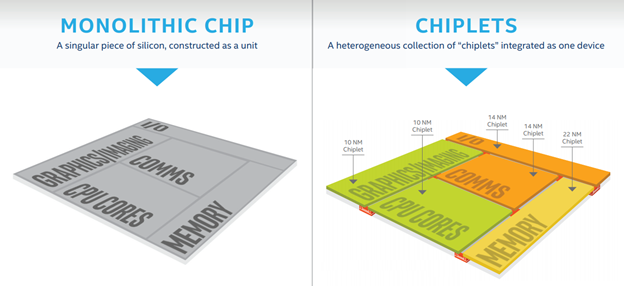

Continuar impulsando el futuro de la Ley de Moore requiere la integración de mejoras en todos los aspectos del proceso de fabricación, no solo a nivel del transistor. Durante décadas, muchos en la industria vieron el empaquetado como simplemente el paso final de la fabricación, el lugar donde hacemos las conexiones eléctricas entre el procesador y la placa base. Sin embargo, esto ha cambiado drásticamente en los últimos años y ahora es un punto crucial en todo el proceso de fabricación.

Hace diez años, el énfasis en la integración de SoC estaba en implementar la funcionalidad de CPU y E/S en el mismo die que una CPU de alto rendimiento. En el futuro, se utilizarán tecnologías de envasado avanzadas para vincular distintos tipos de procesadores, pero sin obligarlos a compartir un solo material de fabricación o nodo de proceso.

Este tipo de desintegración puede parecer, al menos inicialmente, ser la antítesis de lo que se pretende lograr con la Ley de Moore, pero las mejoras de rendimiento y densidad obtenidas al hacer coincidir cada tipo de procesador con su propia implementación de diseño y lógica de transistores de menor ajuste a menudo supera los negativos causados por la separación de un die monolítico en chiplets más pequeños. De hecho, en su artículo original de 1965, Moore afirmó que «puede resultar más económico construir grandes sistemas a partir de funciones más pequeñas que se empaqueten e interconecten por separado».

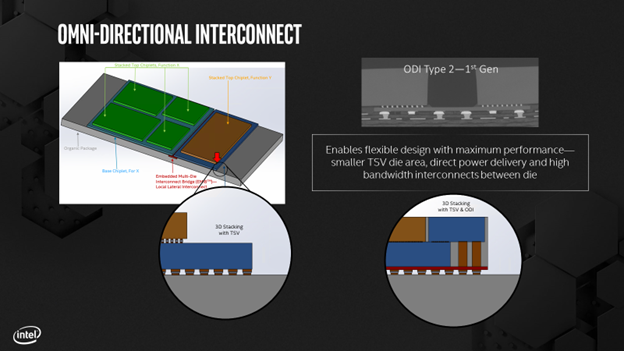

Intel ya ha implementado tecnologías como EMIB (Embedded Multi-die Interconnect Bridge) y Foveros para conectar chiplets en dos y tres dimensiones, como colocar memoria HBM entre CPUI y CPU (como en Kaby Lake-G, con EMIB), o para conectar la matriz de cómputo de 10 nm utilizada en los procesadores Lakefield de Intel cara a cara con la matriz de E/S de 22 nm directamente debajo. También tienen planes de combinar Foveros y EMIB juntos en una tecnología llamada Co-EMIB, en la que se conectan varios chips Foveros 3D a través de EMIB, lo que permite a Intel construir chips mucho más grandes que el tamaño de la retícula para cualquier procesador monolítico y escalar diseños de chips de una manera mucho más amplia que hasta ahora.

Intel ya está mirando, de hecho, más allá del Co-EMIB hacia un nuevo estándar llamado «Interconexión Omnidireccional» (ODI). Uno de los problemas de apilar chips uno encima del otro utilizando métodos existentes como las vías de silicio es que la cantidad de energía que se puede empujar a través de cables tan pequeños es muy limitada. ODI utiliza vías mucho más gruesas para la entrega de energía, al tiempo que ofrece las mismas capacidades que Foveros cuando se implementa para la unión 3D cara a cara.

ODI se puede utilizar para conectar chiplets en una amplia variedad de configuraciones, incluidos escenarios en los que un die está parcialmente «enterrado» y actúa como un puente entre otros dos, o incluso entre dos dies ligeramente superpuestos, con ODI utilizado entre ellos para unos pilares de energía más gruesos, lo que permite que los chips se empaqueten mucho más juntos.

La capacidad de integrar pilas 3D de procesadores presenta otro método para mejorar la densidad del silicio que está totalmente desacoplado del concepto «clásico» exclusivamente centrado en transistores de la Ley de Moore. El escalado monolítico tradicional continuará con los 7 nm con la introducción de EUV, luego los 5 nm y mucho más allá, pero no es el único área en el que Intel espera lidiar con nuevas mejoras de generación en generación tanto en densidad como en rendimiento.

Las mejoras que impulsarán el escalado futuro de la Ley de Moore en Intel no están impulsadas únicamente por reducciones de nodos de proceso o mejoras en la litografía, sino por la colaboración entre múltiples equipos de ingeniería involucrados en diferentes partes del proceso de diseño. Aquí, el estatus único de Intel como fabricante de dispositivos integrados (IDM) es una ventaja, y es que dado que Intel fabrica sus propios productos existe una estrecha colaboración entre los equipos de diseño y los ingenieros que fabrican las piezas. Tenemos así la opción de modificar una arquitectura para que se adapte mejor a las capacidades de un nodo de proceso, o de ajustar un nodo para que coincida con las capacidades que queremos ofrecer en una arquitectura determinada.

No se puede negar que nos enfrentamos a desafíos importantes en la industria, pero el futuro de la Ley de Moore será cualquier cosa menos un lento declive hacia la obsolescencia. Ampliar en alcance de cómo entregamos mejoras de escala generacional ha ampliado las opciones posibles para implementarlas, y en Intel nunca se habían sentido tan optimistas sobre la salud a largo plazo de la Ley de Moore como ahora.

The post El futuro de la Ley de Moore, ¿es todavía brillante? appeared first on HardZone.

[ad_2]