[ad_1]

A pesar de que todavía faltan años de desarrollo e inversión para que la memoria PLC-NAND de 5 bits esté lista para llegar al mercado, ya se están realizando experimentos con memoria de 6 bits por celda con la denominada HLC-NAND (HLC significa Hexa Level Cell precisamente por los seis bits por celda). Kioxia ya ha demostrado que este experimento es real y que funciona, pero pro ahora solo lo han logrado manteniendo un enfriamiento mediante nitrógeno líquido.

Ha sido el departamento de I + D de Kioxia (anteriormente conocido como Toshiba Memory) quienes han compartido sus hallazgos e investigaciones relativas a la memoria NAND Flash de 6 bits por celda, un objetivo marcado que permitirá un escalado de la densidad de memoria hasta unas cotas nunca vistas y que podría, potencialmente, convertirse en el futuro del almacenamiento a medio plazo siempre y cuando consigan llevar estos hallazgos a buen término.

Memoria de 6 bits por celda… pero con nitrógeno líquido

Los avances en cuanto a la memoria NAND Flash están orientados, como es por otra parte lógico, hacia conseguir una mayor densidad y para ello deben ser capaces de almacenar una mayor cantidad de bits por celda. Ahora los investigadores de Kioxia han demostrado que es posible conseguir una celda de memoria de 6 bits que funciona, pero con unos requisitos de refrigeración que obviamente no lo hacen viable para el mercado de consumo, al menos por ahora.

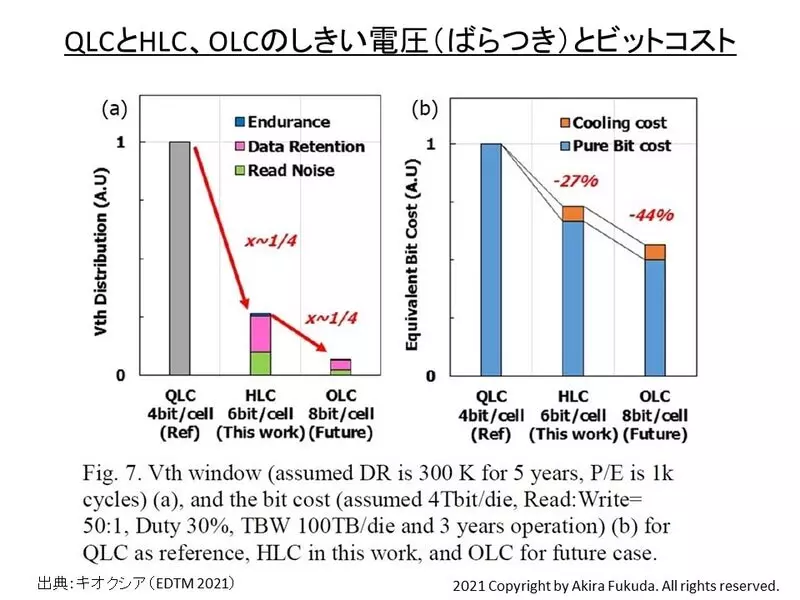

El número de estados necesarios se duplica con cada bit: en memoria SLC NAND con 1 bit es de 2 estados, con MLC de 2 bits son 4 estados, con TLC de 3 bits son 8 estados y con QLC de 4 bits por celda son 16 los estados (con PLC de 5 bits por celda los estados son 32, aunque esta tecnología todavía no es comercial), por lo que la memoria HLC-NAND tendría 64 estados. Cuantos más estados hay que diferenciar, más compleja y lenta es la programación o escritura en la celda de memoria, así que el rendimiento y la durabilidad disminuyen al mismo ritmo al que aumenta la densidad.

Por lo tanto, el rendimiento y la durabilidad disminuyen de manera análoga y aumentan al mismo tiempo los requisitos para la corrección de errores; para mapear la información de 6 bits se requieren 64 estados de voltaje dentro de cada celda tal y como hemos explicado antes, y esto por el momento también causa una temperatura de funcionamiento que requiere una refrigeración extrema para que sea posible.

Para lograr 64 estados de voltaje con la tecnología 3D NAND actual, el chip tuvo que sumergirse en nitrógeno líquido a 196ºC bajo cero, algo necesario para reducir las fluctuaciones del voltaje (el llamado ruido de señal) así como la pérdida de electrones por la emisión termoiónica. Se dice que la durabilidad de la celda HLC se incrementó de 100 a 1.000 ciclos de lectura con este método, lo que corresponde aproximadamente al nivel de las celdas QLC de 4 bits que, sin embargo, no requieren de esta refrigeración extrema.

La memoria PLC de 5 bits llegará primero

Antes de que llegue la memoria HLC-NAND de 6 bits por celda, primero tiene que llegar el paso anterior, la memoria Penta Level Cell (PLC) con 5 bits por celda de memoria. En este ámbito también Kioxia está investigando una solución práctica junto con su socio Western Digital, y hace dos años ya hablaron sobre ello en una conferencia durante el Flash Memory Summit 2019. Unos meses más tarde, Kioxia presentó «Twin BiCS Flash«, un nuevo tipo de estructura que debería permitir más de 4 bits por celda, incluyendo PLC.

Por el momento esta solución parece estar todavía lejos de estar al alcance; el director de tecnología de Western Digital, Siva Sivaram, dijo en junio que no espera que la memoria PLC no llegue al mercado hasta la segunda mitad de la década actual (es decir, hasta como poco 2026), y por lo tanto si todavía estamos lejos de la memoria PLC, imaginad de la HLC de 6 bits.

En cualquier caso, los fabricantes por ahora se están centrando en ofrecer una mayor cantidad de capas apiladas una encima de otra en lo que se conoce como NAND 3D para aumentar la densidad de memoria y reducir los costes de las obleas. Actualmente la industria ya ha logrado alcanzar las 176 capas en chips de memoria funcionales, y fabricantes como Samsung ya juguetean con más de 200 capas, afirmando al mismo tiempo que se han marcado como objetivo llegar a 1.000 capas.

The post Olvida los SSD baratos, PLC parada y HLC ¡necesita nitrógeno líquido! appeared first on HardZone.

[ad_2]