La arquitectura AMD Zen 4 es la cuarta generación de la arquitectura AMD Zen y trae consigo una serie de cambios importantes respecto a la anterior generación y también una serie de novedades concretas. Todas ellas con el objetivo de aumentar el rendimiento sobre Zen 3 y mostrarse competitivos frente a una Intel que está poniendo toda su carne en el asador. ¿Qué novedades trae la arquitectura AMD Zen 4? Os la explicamos.

Han pasado varios años desde que AMD lanzará sus primeros procesadores Ryzen 1000 basados en su arquitectura Zen de primera generación. La cual supuso un cambio de suerte para la empresa liderada por Lisa Su y que AMD dejará de ser vista como una marca de CPUs baratas siempre a remolque de Intel. A día de hoy las arquitecturas de AMD no solamente pueden intercambiar golpes con las de Intel, sino también superarlas en varios aspectos.

En el caso de Zen 3 ha supuesto que la tortuga AMD haya superado a la liebre Intel. La cual se ha dado cuenta del peligro que resulta una AMD que le ha recortado cuota de mercado en procesadores x86 en los diferentes segmentos del mismo en el que compiten de tú a tú. Pero pese a su eventual ventaja, AMD no puede permitirse estar dormida en un mercado de continuo cambio y evolución donde dormirse en los laureles es directamente salir de la carrera e incluso desaparecer. Es por ello que AMD ha diseñado Zen 4 con cambios importantes respecto a Zen 3 y que engloba varias gamas de sus procesadores.

Configuración de los núcleos en Zen 4

La arquitectura Zen engloba los núcleos en un algo que AMD llama CCX, el cual consiste en una serie de núcleos con las siguientes características:

- Cada núcleo tiene la caché de primer y segundo nivel privada, es decir, el resto de núcleos no pueden acceder.

- La caché L3 es compartida y tienen acceso a ella todos ellos. Además, los diferentes núcleos se comunican internamente a través de una red de interfaces Infinity Fabric.

- En Zen y Zen 2 cada CCX estaba compuesto por 4 núcleos y su L3 compartida. En Zen 3 se pasó de 4 a 8 núcleos. Zen 4 tendrá el mismo tipo de configuración que Zen 3 y por tanto 8 núcleos por CCX.

Otra diferencia es que la arquitectura Zen 4 está diseñada para fabricarse bajo el nodo de 5 nm de TSMC, el cual tiene unas reglas de diseño distintas a las de su nodo de 7 nm. Por lo que cualquier chip que utilice los núcleos Zen 4 se basará en dicho nodo de fabricación. Ya sea un chiplet CCD o una APU monolítica.

La arquitectura Zen 4 integrará instrucciones AVX-512

La primera novedad importante estará en el soporte para instrucciones AVX-512, las cuales hasta ahora habían sido exclusivas de las CPU de Intel. Dichas instrucciones como su nombre indica son instrucciones SIMD de 512 bits de longitud, la más larga hasta ahora que han sido utilizadas en una CPU con arquitectura x86. Además las instrucciones AVX-512 contienen diferentes extensiones para diferentes aplicaciones. ¿Las extensiones AVX512 soportadas por los núcleos Zen 4? Son las siguientes

- AVX512VL

- AVX512BW

- AVX512CD

- AVX512_IFMA

- AVX512DQ

- AVX512F

- AVX512_VPOPCNTDQ

- AVX512_BITALG

- AVX512_VNNI

- AVX512_VBMI2

- AVX512_VBMI

- AVX512_BF16

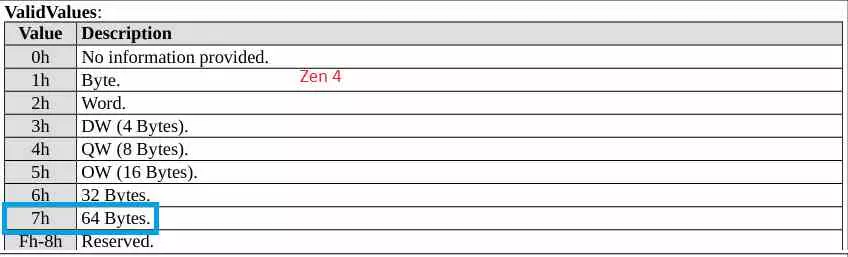

Además, la implementación de las instrucciones AVX-512 en Zen 4 supone que las líneas de la caché de datos de primer nivel y posteriores niveles de caché han aumentado el tamaño de la línea de caché de 32 a 64 bytes o 512 bits. Lo cual es esencial para tomar todos los datos para una instrucción AVX-512 de un solo ciclo. Esta pequeña mejora no solamente significa el soporte para instrucciones AVX-512, sino que el ancho de banda de las unidades Load/Store de la CPU ha aumentado y con ello el ancho de banda interno del procesador. Además que el hecho de que Zen 4 pueda cargar 64 bytes de datos de manera directa supone que hay una nueva unidad AVX-512 capaz de realizar estas instrucciones en un solo ciclo.

Las instrucciones AVX-512 no obstante contienen una limitación y es su alto nivel de consumo, Esto podría hacer que las CPU Zen 4 funcionarán por debajo de sus velocidades de reloj habituales al hacer uso de este tipo de instrucciones.

Cambios en el sistema de caché en la arquitectura Zen 4

| Caché | AMD Zen 4 | AMD Zen 3 |

|---|---|---|

| L1 Datos | 32 KB 8-Way | 32 KB 8-Way |

| L1 Insruccciones | 32 KB 8-Way | 32 KB 8-Way |

| L2 | 1 MB 8-Way | 512 KB 8-Way |

| L3 | 32 MB 16-Way | 32 MB 16-Way |

| L1 ITLB (MMU) | 64 entradas totalmente asociativas | 64 entradas totalmente asociativas |

| L1 DTLB (MMU) | 512 entradas 4.Way | 512 entradas 4.Way |

| L2 ITLB (MMU) | 72 entradas totalmente asociativas | 64 entradas totalmente asociativas |

| L2 DTLB (MMU) | 3072 entradas 12-way | 2048 entradas 8-way |

Desde el primer AMD Zen el sistema de caché de las CPU de AMD se ha mantenido más o menos igual. A excepción de la caché de último nivel que es compartido por todos los núcleos del CCD, pero en el caso de Zen 4 va a haber cambios en lo que es la estructura de cachés del propio núcleo, los cuales podéis ver en la siguiente tabla.

El primer cambio a destacar es en la caché L2 de cada núcleo, esta aumentará la capacidad de los 512 KB hasta 1 MB de memoria, lo que aumenta las posibilidades de encontrar los datos en dicha caché, pero en cambio las cachés L1 y L3 se mantienen sin cambios en cuanto a su tamaño. Eso si, como hemos comentado antes el tamaño por línea de caché ha pasado de los 32 bytes de tamaño a los 64 bytes.

También hay cambios en los búferes TLB o de traducción anticipada. La unidad MMU de cada núcleo del procesador los utiliza para trasladar las direcciones virtuales a direcciones físicas. Como se puede ver en la tabla que inicia esta sección, el búfer de traducción anticipada de la caché de datos de primer nivel ha pasado de 64 entradas a 72 entradas. El de la caché L2 en cambio ha pasado de las 2048 entradas a las 3072 entradas. Lo que supone un aumento del 50% en ese aspecto y no solo en capacidad, sino también en la cantidad de accesos simultáneos.

Soporte para memoria RAM vía Compute Express Link

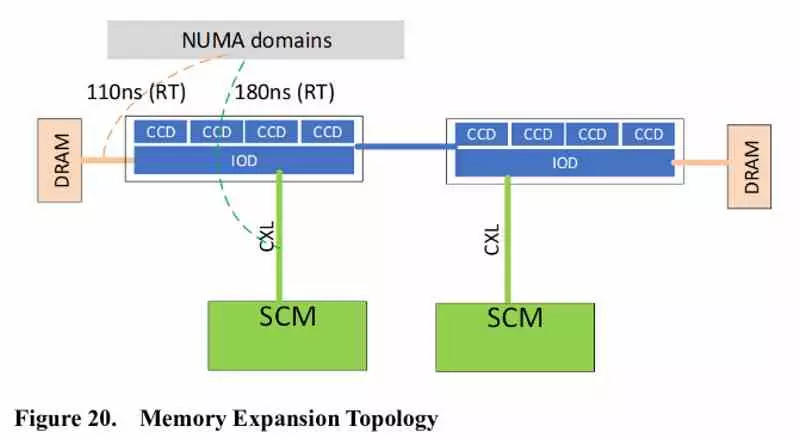

Aquí es donde tenemos que empezar a diferenciar la gama de procesadores para portátiles y escritorio de los futuros AMD EPYC bajo el nombre en clave Genoa y es que mientras que el estándar PCI Express 5.0 no estará disponible para las CPU bajo socket AM5 sí que lo estará en las CPU para servidores y HEDT de AMD basadas en Zen 4 y con ello el soporte para CXL.

La clave del estándar CXL es que le da coherencia con la memoria a la interfaz PCI Express 5.0, lo que significa que los módulos de memoria ya sean memoria no volátil, RAM o una combinación de las mismas no solo se pueden conectar a través de la clásica interfaz de memoria, sino también a través del puerto PCI Express.

En el mercado ya existen módulos de expansión de memoria RAM a través de PCI Express con CXL, llamada también como Storage Class Memory o SCM. AMD va a integrar en sus AMD EPYC Genoa la capacidad de expandir la RAM del sistema a través de la interfaz PCIe 5.0. Eso sí, con la contrapartida de una mayor latencia en el acceso a dicha memoria en comparación a la DDR5, LPDDR5 o cualquier otro tipo de memoria compatible con la que AMD haga compatible las CPU y APU con arquitectura Zen 4.

El uso de dos pozos de memoria distintos a nivel físico supone también la implementación de mecanismos DMA para copiar los datos desde los dos espacios de memoria, los cuáles pese a estar unificados a nivel de direccionamiento no lo están a nivel físico, lo que hace que necesiten un mecanismo para la copia de datos de un espacio de RAM al otro.

Mayor ancho de banda interno y externo

Existe un detalle que no se ha dicho en todo esto y es que AMD hace uso de su interfaz Infinity Fabric para comunicar tanto de manera interna como de manera externa los diferentes componentes. Las interfaces IF con un ancho de banda de 32 bytes han servido para comunicar las caches entre sí durante varias generaciones de los AMD Zen y el salto de los 32 Bytes por línea de caché a los 64 Bytes supone también un salto en ese aspecto y que la cantidad de datos que circulan por dentro de las CCD y CCX con arquitectura Zen 4 se ha duplicado respecto a Zen 3.

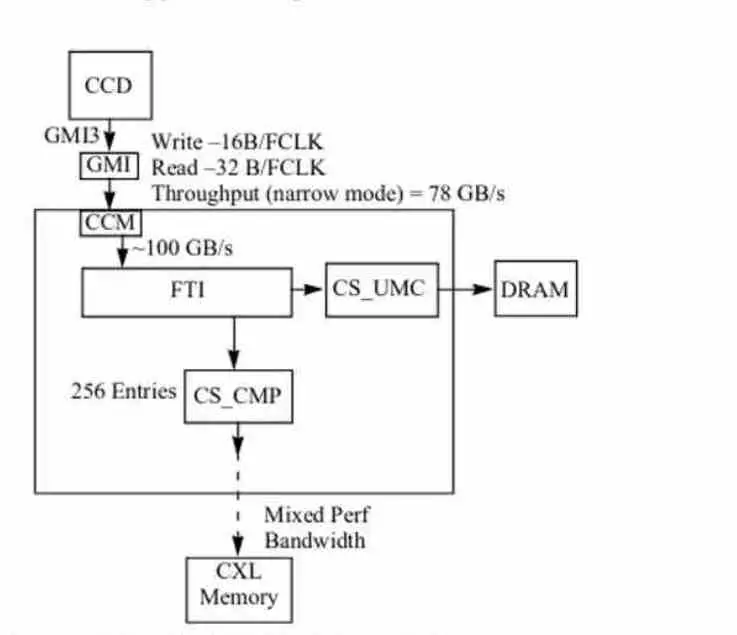

No obstante en cuanto a la comunicación con el Northbridge o IOD no parece que vaya a haber cambios y el puerto GMI que comunica los CCD Chiplets que contendrán los núcleos Zen 4 seguirá teniendo un bus de 16 bytes/ciclo para escritura y de 32 bytes/ciclo para lectura a la velocidad de reloj del IOD. La cual recordemos que en la arquitectura Zen depende de la velocidad de reloj del controlador de la DRAM utilizada. En el diagrama extrapolando los anchos de banda podemos deducir que la velocidad de reloj del IOD es de 2400 MHz, lo cual corresponde con el memclk de la DDR5-4800.

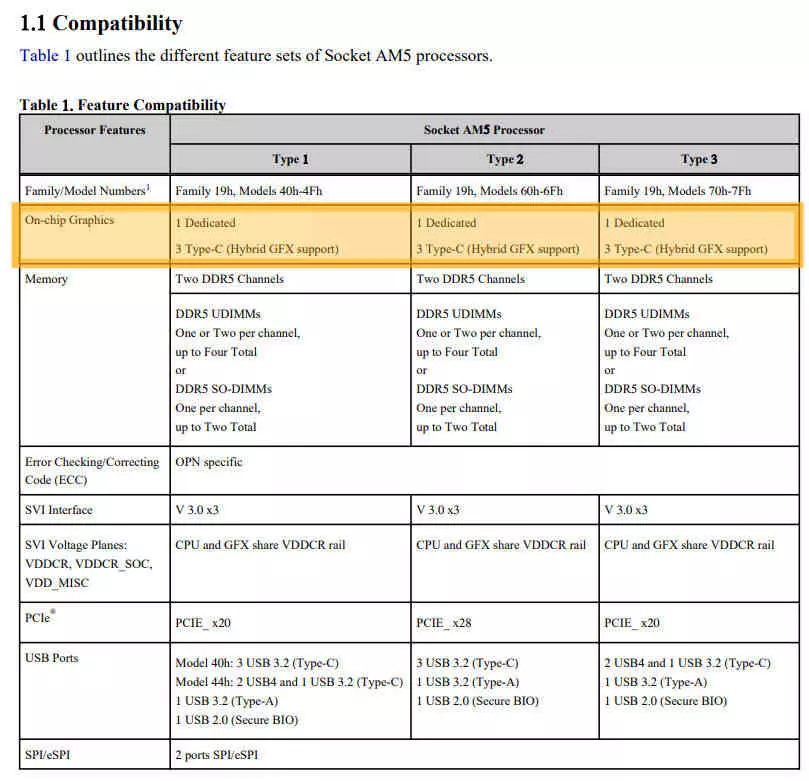

Tampoco nos podemos olvidar del IO Hub. El cual se encuentra también en el IOD o Northbridge y se encarga de comunicarse con los periféricos. Siendo una de las partes que también ha recibido mejoras como consecuencia del soporte de las nuevas interfaces de E/S. Como es caso del USB4 y el PCI Express 5.0. Por lo que AMD ha aumentado su ancho de banda de los 750 MHz a los 1150 MHz.

Lo cual sirve para que la cantidad de líneas PCIe 4.0 máxima haya pasado de las 24 líneas a las 28 líneas. Esto se traduce en que los fabricantes de placas base pueden integrar una segunda unidad SSD M.2 NVMe o una interfaz USB 4. Claro está que estas 4 líneas adicionales no estarán disponibles en todos los chipsets compatibles con Zen 4 tal y como se puede ver en la tabla que acompaña a estos dos últimos párrafos.

The post Los secretos de las CPU AMD Zen 4, ¿cómo aumentan su rendimiento? appeared first on HardZone.